# Calculation of Gate Capacitance in Metal Oxide Semiconductor Field Effect Transistors

### Abstract

In the present work, authors have calculated the inversion layer capacitance and depletion layer capacitance in MOSFET . Depletion layer capacitance is determined by depletion layer thickness  $(t_{\rm di})$  where solution of Poisson's equations have an important role.

### Keywords: Gate Capacitance, MOSFETs.

#### Introduction

The drain current is controlled by applied electric field or gate voltage in MOSFET [1]. The MOSFET is divided in two categories viz enhancement MOSFET and DEMOSFET. DEMOSFET means depletion enhancement MOSFET. DEMOSFET operates in both depletion and enhancement mode. When gate voltage is negative for N channel DEMOSFET, it operates in depletion mode and when gate voltage is positive for N channel DEMOSFET then it operates in enhancement mode. The drain current  $(I_d)$  flows even when gate source voltage  $(V_{\alpha s})$  is zero because a channel exists between drain and source .We apply both negative and positive gate voltages in MOSFET because it is insulated from the channel. The gate (SiO<sub>2</sub>) and channel form a parallel plate capacitor. When MOSFET operates with positive bias gate voltage, the drain current does not exist even when some positive  $V_{ds}$  is applied. In order to obtaine the significant amount of drain current, we need to apply sufficiently high positive gate voltage. This voltage is found to produce a thin layer of free electrons very close to the metal oxide (SiO<sub>2</sub>) film which stretches all the way from source to drain. This thin layer of p-substrate touching the metal oxide film provides the channel for electrons ( acts like N-type material) is called N-type inversion layer or virtual N-channel. The minimum gate-source voltage which produces this P or N-type inversion layer to start the flow of drain current is called threshold voltage (V<sub>gs(th)</sub> or  $V_{th}$ ). When  $V_{gs} < V_{th}$  then  $I_d$ =0. Drain current start only when  $V_{gs} > V_{th}$ . In this work we determine the inversion layer capacitance (Cinv) for two different dielectric materials SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> with dielectric constant 3.9 and 7 respectively. The Poisson's equation is useful for calculating the depletion layer thickness. In turn, depletion thickness t<sub>di</sub> is helpful in determining the depletion layer capacitance C<sub>di</sub>.

**Objective of the study** When we explain the MOSFETs features, we should have in mind the various capacitances affects the speed of MOSFETs in different operational mode. Such type of capacitances are parasitic capacitances. Influence of such type of capacitance on MOSFET operation is given by [2-3]. Other type of capacitances are inversion layer capacitance and depletion layer capacitance. The gate of MOSFET can be considered to be a capacitance. The gate voltage of a MOSFET does not increase unless its gate input capacitance is charged and the MOSFET does not turn on until its gate voltage reaches to the gate threshold voltage ( $v_{th}$ ). This threshold voltage is a minimum voltage which creates a conduction channel between source and drain regions [4]. When MOSFET in operation mode, it is essential to calculate the inversion layer capacitance ( $C_{inv}$ ) and depletion layer capacitance ( $C_{di}$ ).

## Review of Literature

The gate capacitance in MOSFET is important parameter for performance of the devices made by MOSFETs. The parasitic capacitance in MOSFET is calculated by Nebi Caka and Neha Srivastava [2-3]. At present scenario as technology improves, the dimensions of the devices decrease, so there are more challenges created in determining the

Hemendra Kumar Assistant Professor, Dept. of Physics, M.M.H.College, Ghaziabad, U.P., India

Sanjeet Pratap Singh

Assistant Professor, Dept. of Physics, M.M.H.College, Ghaziabad, U.P., India

### E: ISSN NO.: 2455-0817

parameter of the devices. The dimensions of devices shrink in nano scale such as corbon nanotube field effect transistors. The gate capacitance of carbon nanotube field effect transistor is calculated by H. kumar [5].

$$C_g = e \frac{dN_e}{dV_g}$$

When the bulk material dimensions shrink in nano scale, its features drastically change. So it is very difficult to estimate the charecteristics of the devices. However many charecteristics such as energy band gap, specific heat of nano device are calculated by Hemendra kumar [6].

### Concepts

We know that if any tiny particle moves, a wave gets associated with it. All these problems are dealt with wave function whoes solution is given by Schroedinger equation.

$$-\frac{\hbar^2}{2m_e}\frac{d^2\psi}{dx^2}+\varphi(x)\psi=E\psi$$

In this paper the Poisson's equation which is useful tool for determining the depletion layer thickness  $t_{di}$ , the boundary conditions for the Poisson's equation are

$$\frac{d^2\Phi}{dz^2} = \frac{\left[\rho_{depl}\left(t\right) - e\sum N_i\xi^2(t)\right]}{K_{sc}\varepsilon_0}$$

# VOL-3\* ISSUE-12\* (Part-2) March- 2019 Remarking An Analisation

The term  $d\phi/dt$  from that equation disappears for large depletion layer thickness  $t_{di}$ . Research Design

# Calculation of inversion layer capacitance (C<sub>inv</sub>)

To find the value of  $C_{inv}$ , we apply the self consistant solution. The first numerical self consistant calculation for inversion layers were made by Howard and Stern [7].

$$C_{inv} = \frac{eN_{inv}}{F_c}$$

Where  $F_s$  is the silicon surface potential given by equation

$$F_{s} = \frac{e[N_{inv} + N_{depl}]}{K_{sc}\mathcal{E}_{0}}$$

Thus inversion layer capacitance C<sub>inv</sub> is given by

$$C_{inv} = \frac{N_{inv}.K_{sc}.\mathcal{E}_0}{N_{inv} + N_{depl}}$$

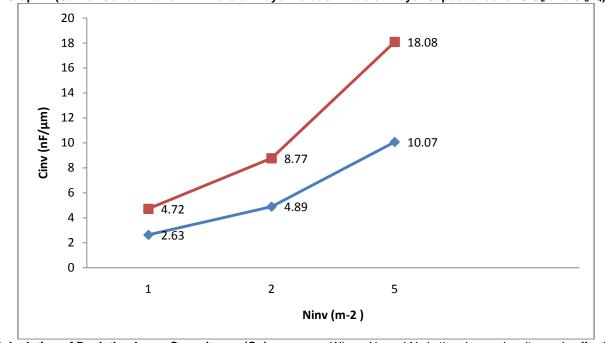

Now we calculate the  $C_{in\nu}$ , the different dielectric materials for  $SiO_2$  and  $Si_3N_4$  with dielectric constant of these semiconductors ( $K_{sc}$ ) are 3.9 and 7 respectively with given parameters in table 1. The graph is ploted between  $C_{in\nu}$  and  $N_{in\nu}$  as shown in figure 1.

Table-1 Value of C<sub>inv</sub> with different N<sub>inv</sub> at constant N<sub>depl</sub>

|         | S.No.                                                                                                              | N <sub>inv</sub> (m <sup>-2</sup> ) | N <sub>depl</sub> (m <sup>-2</sup> ) | For SiO <sub>2</sub><br>C <sub>inv</sub> (nF/μm) | For Si₃N₄<br>C <sub>inv</sub> (nF/µm) |  |  |  |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------------------------------|--------------------------------------------------|---------------------------------------|--|--|--|--|--|

| 1       |                                                                                                                    | 1 X 10 <sup>14</sup>                | 1.213 X 10 <sup>15</sup>             | 2.63 X 10 <sup>-3</sup>                          | 4.72 X 10 <sup>-3</sup>               |  |  |  |  |  |

| 2       |                                                                                                                    | 2 X 10 <sup>14</sup>                | 1.213 X 10 <sup>15</sup>             | 4.89 X 10 <sup>-3</sup>                          | 8.77 X 10 <sup>-3</sup>               |  |  |  |  |  |

| 3       |                                                                                                                    | 5 X 10 <sup>14</sup>                | 1.213 X 10 <sup>15</sup>             | 10.07 X 10 <sup>-3</sup>                         | 18.08 X 10 <sup>-3</sup>              |  |  |  |  |  |

| Graph ' | Graph 1 (Carrier Concentration in Inversion Layer versus Inversion Layer Capacitance for SiO $_2$ and Si $_3N_4$ ) |                                     |                                      |                                                  |                                       |  |  |  |  |  |

Calculation of Depletion Layer Capacitance (C<sub>di</sub>) To calculate the depletion layer capacitance of a MOSFET, we consider the depletion layer thickness (t<sub>di</sub>) first . This thickness can be calculated by the charge density of the depletion layer i.e.

$$t_{di} = \left[2K_{sc}\mathcal{E}_0\Phi_d/e(N_A - N_D)\right]^{1/2}$$

Where N<sub>A</sub> and N<sub>D</sub> is the charge density ,  $\phi_d$  is effective band bending from the bulk to the surface, apart from the contribution of the inversion layer itself. The boundary conditions for the Poisson's equation  $\frac{d^2 \phi}{dt^2} = \frac{[\rho_{depl}(t) - e \sum N_i \xi^2(t)]}{2}$

$$\frac{d^2 \varphi}{dz^2} = \frac{\left[p_{depl}\left(t\right) - e \sum N_i \zeta\right]}{K_{sc} \varepsilon_0}$$

### P: ISSN NO.: 2394-0344

### RNI No.UPBIL/2016/67980

### E: ISSN NO.: 2455-0817

The term  $d\phi/dt$  from that equation disappear for large t and its value at the surface be  $F_s$  which is useful for considering the inversion layer capacitance. Hence the depletion layer capacitance  $C_{di}$  is given by relation

$$C_{di} = \frac{\varepsilon_0 K_{so}}{t_{di}}$$

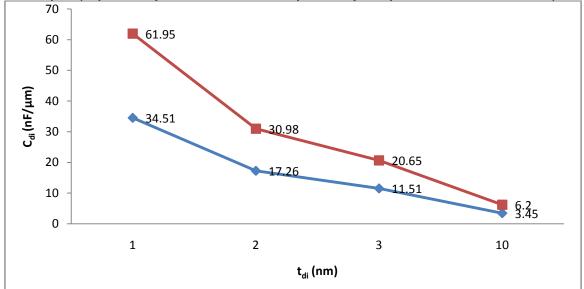

Using parameters given in table 2 for two dielectric materials  $SiO_2$  and  $Si_3N_4$  with dielectric constants (K<sub>sc</sub>) 3.9 and 7 respectively, the graph is ploted between the C<sub>di</sub> and t<sub>di</sub> as shown in figure 2.

| Value of C <sub>di</sub> at different t <sub>di</sub> |                                                                             |                                                                 |                                     |                                      |  |  |  |

|-------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------|--------------------------------------|--|--|--|

| S.No.                                                 | T <sub>di</sub> thickness SiO <sub>2</sub> & Si <sub>3</sub> N <sub>4</sub> | $\mathcal{E}_0$                                                 | For SiO₂<br>C <sub>di</sub> (nF/µm) | For Si₃N₄<br>C <sub>di</sub> (nF/µm) |  |  |  |

| 1                                                     | 1.0 nm                                                                      | 8.85 X 10 <sup>-12</sup> F/m<br>Or 8.85 X 10 <sup>-3</sup> nF/m | 34.51X 10 <sup>6</sup>              | 61.95 X 10 <sup>6</sup>              |  |  |  |

| 2                                                     | 2.0 nm                                                                      | 8.85 X 10 <sup>-12</sup> F/m<br>Or 8.85 X 10 <sup>-3</sup> nF/m | 17.26X 10 <sup>6</sup>              | 30.98 X 10 <sup>6</sup>              |  |  |  |

| 3                                                     | 3.0 nm                                                                      | 8.85 X 10 <sup>-12</sup> F/m<br>Or 8.85 X 10 <sup>-3</sup> nF/m | 11.51 X 10 <sup>6</sup>             | 20.65 X 10 <sup>6</sup>              |  |  |  |

| 4                                                     | 10.0 nm                                                                     | 8.85 X 10 <sup>-12</sup> F/m<br>Or 8.85 X 10 <sup>-3</sup> nF/m | 3.45 X 10 <sup>6</sup>              | 6.20X 10 <sup>6</sup>                |  |  |  |

Tabla

### Conclusion

From Table 1 we observed a trend that when the inversion layer concentration of carriers increases then the value of inversion layer capacitance also increases. This trend is also shown in the graphical repersention (fig. 1). All these results are obtained at constant depletion layer carrier concentration. It is evident from the table 2 that, the depletion layer capacitance decreases with increase of depletion region thickness  $t_{di}$ . Hence we conclude that by controlling the depletion layer thickness  $t_{di}$  or depletion layer capacitance  $C_{di}$ , we can change the MOSFET speed and other features.

### References

- From B.L.Theraja. (2002), P( 410-413), ISBN-81-219-0094-8.

- Nebi Caka, Milaim Zabeli,Myzafere Fimani,Qamil Kabashi (March 2007), "Influence of MOSFET parameters in its parasitic capacitance and their impact in digital circuits' . WSEAS TRANSACTIONS on CIRCUITS and SYSTEMS; issue 3, volume 6, Page;281-287, (ISSN- 1109-2734).

- Neha Srivastava and G.S.Tripathi (December 2011), "Modelling of parasitic capacitances for single – gate, double gate and independent double-gate MOSFET'. International journal of computer applications (0975-8887), Volume 35- No.9, Page;25-31.

- Toshiba (26 July2018), 'MOSFET Gate Drive Circuit Application Note' Toshiba Electronic Devices & Storage Corporation, Page 1-22.

- Hemendra Kumar, Shailendra Gangwar, et. Al. (2010), "Analysis of gate capacitance of carbon nanotube field effect transistor' Acta Ciencia Indica, volume xxxvi, No. 4 Page; 529.

- Hemendra Kumar, Shailendra Gangwar, Sanjeet Pratap Singh, (28-29 December 2017), Determination of energy band gap and specific heat of armchair and zigzag single wall carbon nanotubes' International Conference on Technology & trust (ICTT17) Page; 387-390, ISBN; 978-93-8357-527-5.

- F.Stern, (1968), Phys. Rev. Letters, Volume 21, Page; 1687.